【企業名】サンケン電気株式会社

サンケンエレクトリックコリア株式会社

【住所】埼玉県新座市北野三丁目6番3号

大韓民国ソウル特別市 江西区 麻谷東路 56 建窩ビル 4 階

【発明者】伊藤 公一

姜 韓柱

【発明の名称】PFCバースト制御回路

【技術の詳細】

1. 類似する先行技術

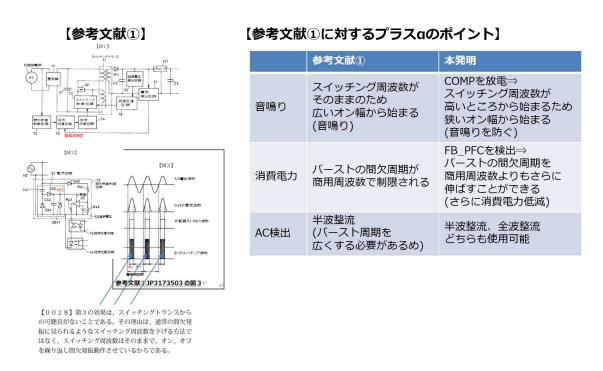

【参考文献①】: JP3173503

2. 先行技術の構造・構成、製法、回路動作などの説明

PFC 電源において、負荷が軽くなった場合に消費電力を下げるため、スイッチングの間欠動作を用いている。従来、PFC の出力電圧を検出する FB 端子電圧を検出し、定常時の出力電圧のうち、任意の値を設けて PFC の出力電圧の制御を行っていた。例えば、JP3173503の図 6 には、軽負荷時、交流電源の整流出力のピーク及びその近傍の期間のみに、スイッチング素子のスイッチングのための発振がなされる様に、発振の間欠制御をなす構成が開示されている。

#### 3. 先行技術の問題点

先行技術である JP3173503 は、軽負荷時、スイッチングを、整流出力のピーク及びその 近傍の期間のみに間欠動作することで、効率をよくする構成が開示されているが、軽負荷時 というだけで、PFC の出力電圧を検出する FB 端子電圧を検出し、定常時の出力電圧のうち、任意の値を設けて PFC の出力電圧の制御ついては、具体的な記載は無く、効率重視で、きめ細やかな動作が出来ないと言った問題がある。また、図3では、定常時の出力電圧のうち、適当なヒステリシス電圧を設けて、この電圧を用いて、制御すると言った技術があるが、AC 電圧を無視する為に、AC 電圧の低い区間でもスイッチングをさせるため、AC 入力電圧が低いときに昇圧動作を始めるタイミングがあり、PFC 出力へのエネルギー伝達効率が 悪いと言った問題があった。つまり、スイッチングの効率と、きめ細やかな制御の2つを満たす技術が無かった。

- 4. 今回の発明の詳細

- (1) 先行技術との相違点

本提案では、先行技術に対し、定常時の出力電圧のうち、検知レベルは任意設定可能であるが、例えば、89%-90%のヒステリシス電圧を設けて、きめ細やかに制御し、更に、AC入力電圧のレベルを検知し、比較的に高い AC 電圧の区間でスイッチングさせることでエネルギー伝達効率をよくする方法を提案する。これにより、スイッチング損失を削減し、きめ細やかなスイッチング制御が可能となり、消費電力を削減することが出来る。入力される

AC電圧の状況に応じて、効果的な期間を選択し、更に、PFC出力電圧を監視して、例えば、89%以上、90%以下といった比較的に狭い期間を選択することで、効率的なスイッチング制御を可能とし、スイッチング損失を抑えることが出来る。

#### (2)発明の実施形態例

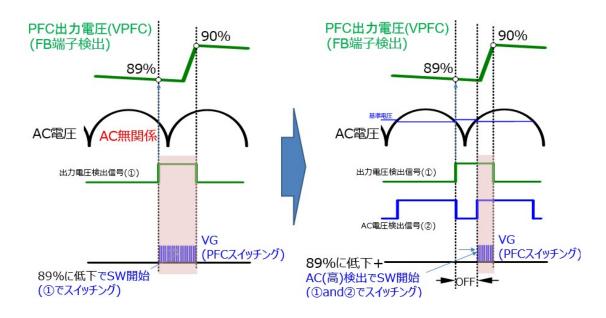

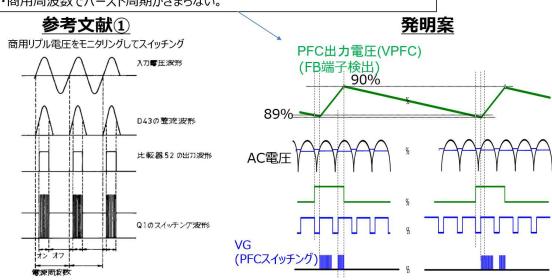

図1は、バースト制御とAC電圧との関係を示す。今回の提案技術を適用したスイッチング波形であって、PFC出力電圧に応じて、89%から90%に昇圧する際のPFCスイッチング期間を示す。左図は、PFC出力電圧をFB端子で検出し、89%以上90以下でアクティブとなる出力電圧検出信号(①)がアクティブであれば、AC電圧とは無関係に、PFCスイッチングを行う場合を示す。右図は、出力電圧検出信号(①)とAC電圧を基準電圧以上か、否かでアクティブとなるAC電圧検出信号(②)が共にアクティブの期間のみに、PFCスイッチングを行うことを示す。右図の方が短い時間で、スイッチングの回数も少なく、昇圧することが出来、効率が良いことを示す。

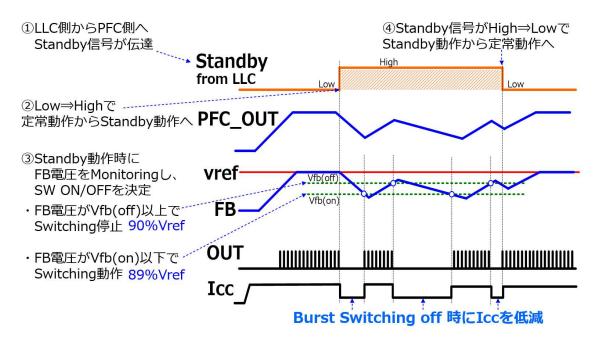

図2は、AC 電圧を無視した PFC バースト制御動作の詳細を示す。図1の左図に示した A C電圧を無視した状態で、スタンバイ信号がアクティブとなった軽負荷の状態で、それぞれの信号について、詳細に示したタイミングチャートを示す。

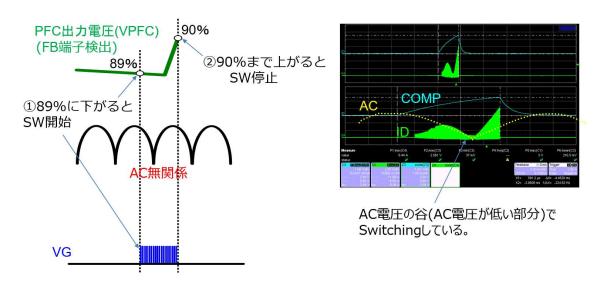

図3は、AC電圧と無関係のPFCバースト制御動作を示す。AC電圧が低いときに昇圧動作を始めるときがあるために、出力へのエネルギー伝達効率が悪い。スイッチング回数が多くなるために、スイッチロスにより消費電力が大きくなる。つまり、消費電力が大きく、効率が悪い。

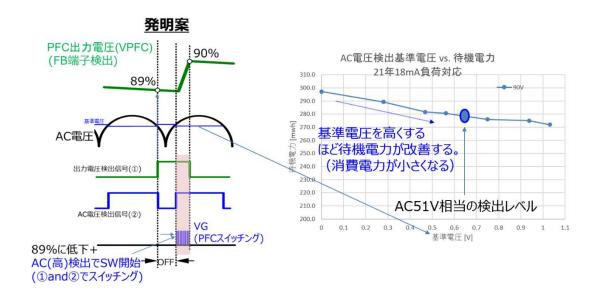

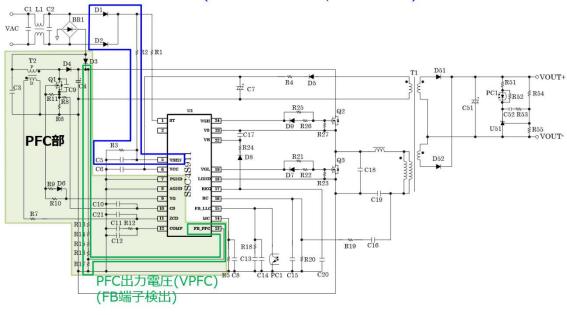

図4は、本実施形態の効果について示した図である。AC電圧に対して、基準電圧高くするほど、待機電力が改善することを示している。消費電力が下がっていることを示している。図5は、本実施形態のアプリケーション回路図を示す。AC電圧のレベルを検知して、スイッチング制御を行う回路図である。具体的なICを用いて、実際の製品における接続関係を示している。

図6は、参考文献①との相違点を示す。本実施例では、全波整流でも半端整流でも使用することが可能である。また、バースト周期を89%から90%電圧レベル、ヒステリシス電圧幅を変更することで変えることが出来、待機電力の調整が可能である。商用の周波数でバーストの周期が決まらないと言った特徴がある。

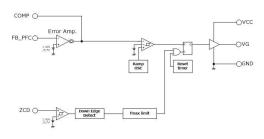

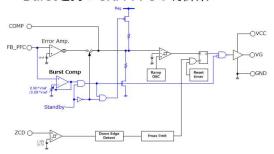

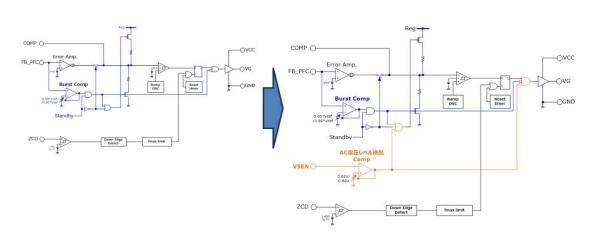

図7は、スタンバイ時の PFC バースト回路を示す。左図が Burst 回路を持たない CRM PFC の制御系を示す回路であって、右図が Burst を持つ CRM PFC の制御系を示す回路である。青色部分が Burst 回路のために、追加された回路を示す。LLC 側から、Standby 信号 (Hi) が伝達されると、定常動作からスタンバイ動作へ移行する。スタンバイ動作時に FB 電圧をモニタリングして Sleep/Wake 状態を決定する。FB 電圧が Vref の 90%以上になると Sleep 状態で内部回路およびスイッチングを停止させる。FB 電圧が Vref の 89%以下になると Wake 状態で内部回路およびスイッチングを動作させる。

図8は、従来のBurst 制御から、AC レベルを見る Burst 制御への追加回路を示す。オレ

ンジ色部分が AC レベルを見るために追加された回路であり、整流回路からの出力は、半波でも全波検出でも対応可能となっている。

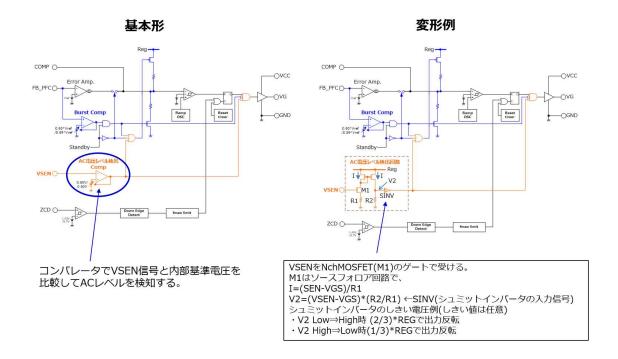

図9は、AC電圧レベル検出回路の変形例を示す回路である。左図は、基本形を示す回路であって、コンパレータで VSEN 信号と内部基準電圧を比較して AC レベルを検知する。右図は、VSEN 信号を NchMOSFET (M1) のゲートで受ける。M1 はソースフォロア回路で、I= (SEN-VGS) /R1、V2=(VSEN-VGS)\*(R2/R1)である。V2 は、SINV(シュミットインバータの入力信号)であって、シュミットインバータのしきい値電圧は、任意である。図 10 は、参考文献①に対するプラス  $\alpha$  のポイントを示す。参考文献①は交流電源の整流出力のピーク及びその近傍の期間のみに、スイッチング素子のスイッチングのための発振がなされる様に、発振の間欠制御をなす構成が開示されている。参考文献①に対する本発明

のプラス α のポイントを示している。音鳴り、消費電力、AC 検出の3点で、利点がある。

図1:バースト制御と AC 電圧との関係

図2:AC電圧を無視したPFCバースト制御動作の詳細

#### 【従来の問題点】

AC電圧が低いときに昇圧動作を始めるときがあるため、出力へのエネルギー伝達効率が悪い。 ⇒スイッチング回数が多くなるため、スイッチングロスにより消費電力が大きくなる。

図3:AC電圧と無関係のPFCバースト制御動作

図4:本実施形態の効果について

#### AC電圧のレベルを検知(下図は全波整流検出,半波検出も可)

図5:本実施形態のアプリケーション回路図

- ・全波整流でも半端整流でも適用可能

- ・バースト周期を89%-90%電圧のレベル、ヒステリシス電圧幅を変更することで 変えることができ、待機電力の調整が可能

- ・商用周波数でバースト周期がきまらない。

図6:参考文献①との相違点

#### Burstを持たないCRM PFCの制御系

### Burstを持つCRM PFCの制御系

図7:スタンバイ時のPFCバースト回路

#### 従来のBurst制御

### 本発明(ACレベルを見る)Burst制御

図8:従来のBurst 制御から、AC レベルを見る Burst 制御への追加回路

図9:AC電圧レベル検出回路の変形例

図 10:参考文献①に対するプラス α のポイント

【企業名】サンケン電気株式会社

【住所】埼玉県新座市北野三丁目6番3号

【発明者】佐藤 憲

【発明の名称】半導体装置

【技術の詳細】

#### 【背景技術】

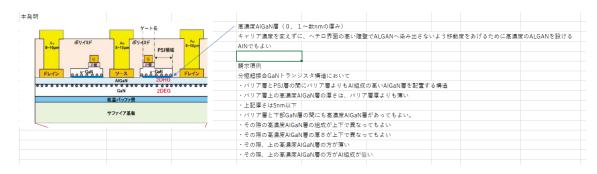

GaN-HEMT の電界強度分布の均一化を目的に PSJ (Polarization Super Junction) 構造が提案されている。例えば、WO2011-162243 号公開。

PSJ 構造の 2DHG は、ゲート電極と接続し、2DEG と SJ 構造を形成し、GD 間の電界強度 分布を均一化させることで、高耐圧化、コラプス対策を行っている。

#### 【発明が解決しようとする課題】

2DHG は、Off 時に空乏化し、On 時にゲートからホールを注入して、キャリアを回復させるという動作を行っている。

しかしながら 2DHG は、2 DEG と比較して移動度が低く回復には時間がかかる。

#### 【発明内容】

そこでバリア層と PSJ 層の間に、バリア層よりも組成の高い AlGaN 層を形成することで、 移動度を改善し、SW 特性を改善させる。

【企業名】サンケン電気株式会社

【住所】埼玉県新座市北野三丁目6番3号

【発明者】三上 祐樹

【発明の名称】半導体発光素子

#### 1. 類似する先行特許

透明電極 6(ITO 電極)の剥離防止と電流拡散を促進させるため、透明電極 6 の側面に傾斜を備える凹部を形成した構造が公知である。

先行特許: JP6011108

#### 2. 先行特許の問題点

ワイヤー周囲のシリコーン樹脂は膨張収縮が大きく,他の半導体デバイスに比べてワイヤーへの負荷が大きく 剥がれやすい。

#### 3. 発明の概要

ワイヤボンディング前に短波長(紫外線)かつ高出力のパルスレーザー光をAu電極に照射することでAu電極の表層を削る(レーザーアブレーション)。Au電極の金属結合を切って、Au電極表面に新生面を露出させることで、レーザー照射した表層は荒れ、Au電極とAuボールとの接合強度を高めることができる。

なお、Ar プラズマ照射の場合、素子全体がスパッタされる問題がある。また、ダイボンド後に高出力のパルスレーザー光を Au 電極に照射すると、パッケージの白樹脂がダメージ(脆化や変色(黄変) )を受ける問題が生じる。

◇案>

W/B前にレーザー照射によってAu表層を削り(レーザーアプレーション)、

Au電極表面に新生面を出すことで、Au - Au 接合強度を強固にしたい。

レーザーパルスを照射

(短波長)

LEDの場合、ワイヤー周囲がシリコーン樹脂であることが多く、他の半導体デバイスに比べ、

膨張収縮が大きいため、ワイヤーへの負荷が大きく剥がれやすい、という課題がある。

Au電極の結合を切る

LED 素子

LED 素子

LED 素子

LED 素子

LED 素子

LED 素子

Au電極の結合を切る

LED 素子

LED 素子

LED 素子

Au電極の結合を切る

LED 素子

LED 表子

LED

アプレーションによって新生面を得ることで

Auボールとの接合が強固になる(と見込んでいます)。

Auボールとの接合が強固になる(と見込んでいます)。

Auボンディングポール

Au電極

Arプラズマ照射は既知技術ではあるが、下記デメリットがある。

・素子全体がスパッタされる

・ダイボンド後に実施するとパッケージ白樹脂がダメージを受ける。一脆化や変色(黄変)がおこる。

#### <欠点>

レーサービーム径を電極サイズ以下 (80μm以下程度) に絞れるか? Au表層を薄く削ぎ落すようなビーム出力が得られるか?強すぎてチップを破壊しないか? 新生面が出ても、表面が荒れることでW/Bし難くならないか?

#### <利点>

2次汚染防止のために、アルゴンや窒素 雰囲気中でレーザー照射するのが良さそうだが Auは反応性が低いので、大気中でも可能と期待できる。

以上

【企業名】サンケン電気株式会社

【住所】埼玉県新座市北野三丁目6番3号

【発明者】丹羽 愛玲

【発明の名称】半導体発光素子

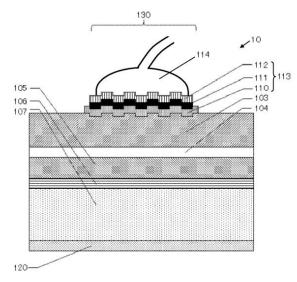

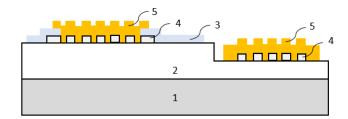

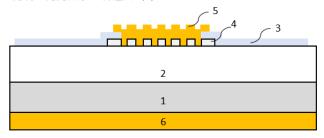

#### 1. 類似する先行特許

発光層を有する半導体層の表面に凹凸加工をする事で、その上の電極の表面にも凹凸加工を施し、光取出し 効率やワイヤーとパット電極部の接触強度を向上させる事を特徴とした発光素子が公知である。

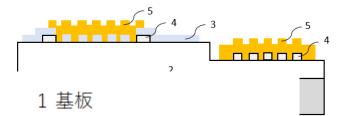

#### 【図1】

先行特許: 特開 2017-34214

#### 2. 先行特許の問題点

しかし、これらの凹凸を得る為には、凹凸加工するフォトリソ工程、エッチング工程を追加し製造する必要がある。また、窒化物半導体はウェットエッチング加工をする事が困難であり、ドライエッチングではエッチングダメージによる窒化物半導体表面の結晶劣化が発生してしまう為、半導体層の表面の凹凸加工は現実的ではない。

#### 3. 発明の概要

今回の発明の発光素子は、発光層を有する半導体積層体(2)の表面に導電透明電極部(3)、電流ブロック層部(4)、パット電極部(5)が形成される発光素子である。

パット電極部(5)直下の電流ブロック層部(4)に凹凸加工をする事で、パット電極部(5)表面に凹凸を設けられ、 光取出し効率を維持しながらワイヤーとパット電極部(5)の接触強度も向上させる事が可能である。

また、パット電極部(5)下の導電透明電極部(3)において凹凸加工を設けても、ワイヤーとパット電極部(5)の接触強度も向上させる事が可能である。

どちらも既存設計で必要な機能をもった層であり、窒化物半導体表面に凹凸加工を施さない為、追加工程を必要 としない事が特徴でもある。

#### 発明の発光素子の構造図(1)

発明の発光素子の構造図 (3)

発明の発光素子の構造図 (2)

- 2 半導体積層体

- 3 導電透明電極

- 4 電流ブロック層

- 5 パット電極(SiO2,SiN)

- 6 裏面電極(ITO)

以上

【企業名】サンケン電気株式会社

【住所】埼玉県新座市北野三丁目6番3号

【発明者】近藤 太郎

【発明の名称】半導体装置

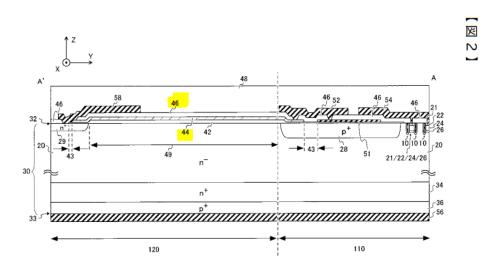

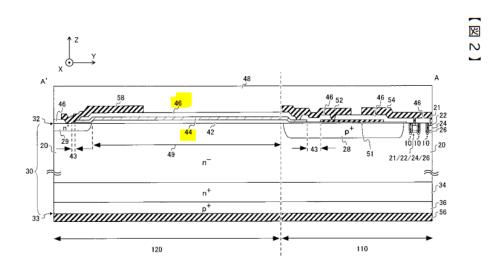

#### 1. 類似する先行特許

ゲート配線52と終端電極58との間を抵抗性窒化シリコン膜44でつないだ構造が公知である。この構造において、抵抗性窒化シリコン膜44の効果として、基板表面電荷による空乏層の広がりの影響を低減する効果が記載されている。ただし、平面的に見て、窒化シリコン膜44はとぐろ形状に形成されている。

先行特許:特開2017-92360

#### 2. 先行特許の問題点

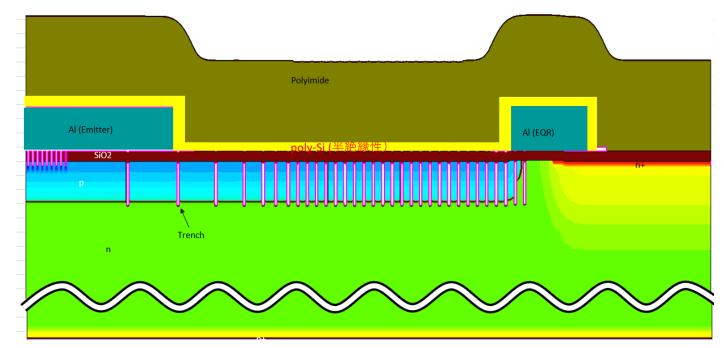

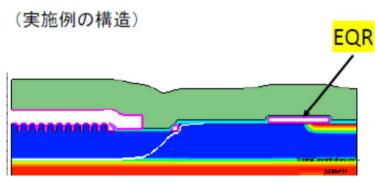

耐圧改善領域に外周トレンチ構造を設けた例がある。外周トレンチ構造はそもそも上記先行特許のような半絶縁性膜を基板上に設けないので、キャリアトラップによるリークは生じにくい。しかし、近年、デバイスの高性能化に伴い、半導体デバイスの樹脂中に含まれる不純物種が多彩となり、樹脂からデバイス外周部への可動イオン侵入による信頼性劣化が問題となっている。既存のトレンチ型外周構造では外周トレンチ上に酸化膜を形成し、その上に Polyimide などの保護膜を形成するのが一般的である。外周トレンチが設けられた半導体基板上に設けられる Polyimide-SiO 界面に外来電荷があると、外周トレンチ内の電極はフローティング電位であるため、外来電荷の影響を受けて、その電位が変動しやすくなり、半導体装置は耐圧変動を起こりやすい。

#### 3. 発明の概要

外周トレンチ上部に半絶縁性を有した poly-Si を保護膜として形成して、さらにこの poly-Si 保護膜の一方をエミッタ電極に接続し、poly-Si 保護膜の他方を EQR 電極に接続する。この poly-Si 保護膜は半絶縁性のため、リーク電流はナノオーダー以下となる。また、この poly-Si 保護膜はエミッタ電極や EQR 電極に接続されているため、樹脂からの可動イオンが蓄積されず、外来電荷の影響を受けて外周トレンチ内の電極の電位が変動する問題に対する信頼性耐量を向上させることができる。

なお、半導体装置を平面的に見て、poly-Si 保護膜は、半導体素子を囲み、エミッタ電極と EQR 電極との間をゲートバスラインが間にある場合はその外側に設けられているように配置する。

発明構造の断面図

以上

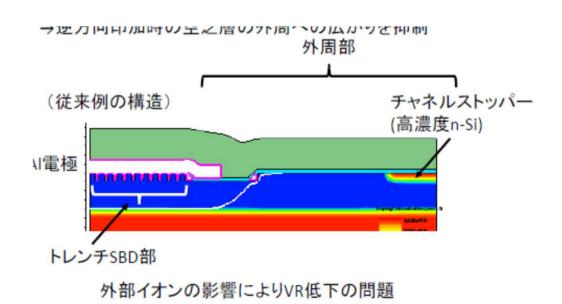

【社内書式番号】2023-056 【企業名】サンケン電気株式会社 【発明者】鹿内 洋志 犬飼 早紀 【発明の名称】トレンチSBD信頼性

# 【技術の詳細】

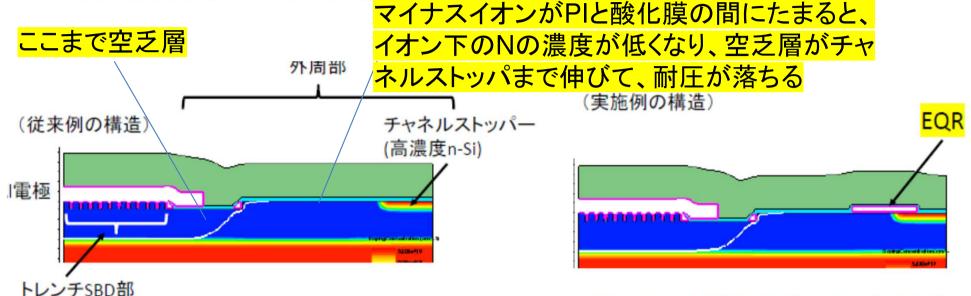

**く従来技術**>半導体において外部負イオンの影響による耐圧劣化を改善するために 保護膜厚を厚くする方法がある。

### <課題>

保護膜を厚くした場合、コストがかかる。応力の問題で、厚くできない。

## <本発明>

・チャネルストッパーに電気的に接続したEQR(Equivalent Potential Ring)をチャネルストッパーより内側へ延長して形成することで、耐圧劣化を防ぐ。

外部イオンの影響を抑制しVR低下問題改善

## (効果)

外部負イオンの影響によるVR低下を抑制できる

→逆方向印加時の空乏層の外周への広がりを抑制

外部イオンの影響によりVR低下の問題

外部イオンの影響を抑制しVR低下問題改善

- •EQRでチャネルストッパまで空乏層が伸びにくくなる。

- ・PI(緑)はイオン遮蔽しない。水色とPIの界面

- ・EQRは裏面と同電位

- •ERQの材料 ポリSi、Al,Ni等

- •EQRはマスクの幅より4um以上出っ張る

- •120Vの本命構造。試作して効果が出ている。Siに限定せずTrench SBD 以外でもOK。用途:電源二次側整流。チップ、玉形、Assy 堀松、中国。出願するなら日中+アルファで考えている。

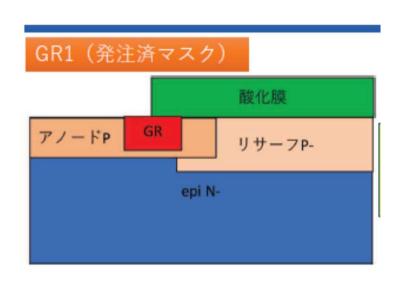

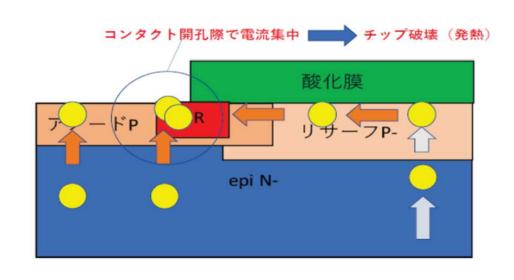

【社内書式番号】2023-060 【企業名】サンケン電気株式会社 【発明者】犬飼 早紀 鹿内 洋志 【発明の名称】 幅広トレンチSBD 構造

# <技術の詳細>

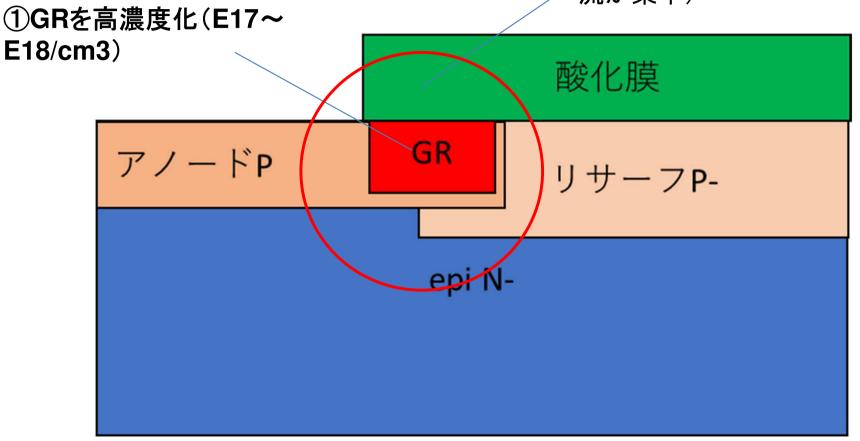

【従来技術】FRDにおけるリカバリー動作時の破壊耐量を向上する構造で、ダイオードチップの端部(アノード拡散層端部)に、GR層と、リサーフを形成する構造がある。

### 【課題】

FRDをリカバリー動作させたとき、外周領域のドリフト層から引き抜かれたホールがSi表面付近を通って、表面電極と接触しているコンタクト開孔際に電流が集中する。コンタクト開孔周辺のSi表面付近の抵抗が高い場合、集中した電流によって発熱し素子が破壊する懸念がある。

## く従来構造>

## 【技術の詳細】

本発明 ①②を実施する構造

②酸化膜でGRを覆う(高濃度のGRに電極が接触すると、電流が集中)

$GR(E17\sim E18) > TJ-F>(E16) > Resurf(E15)$